Cerium systems fresher recruitment Interview Questions [1hr]

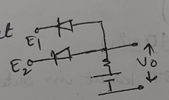

1) What is FPGA ? 2) What is difference between ASIC and FPGA ? 3) Can we replace FPGA with ASIC ? 4) What FPGA consists of actually ? 5) Tell the flow of FPGA like how we will implement a code on FPGA ? 6) What are Universal gates? Implemented NOR gate using Nand gate? Is Mux Universal gate ? If yes implement And & Or gates using 2:1 mux ? 7) Basic diff between Latch & FF ? 8) Make a D latch using 2:1 Mux ? 9) Implement the ckt for 101 pattern detecting don't use the FSM but implement in sequential ? 10) Draw the CMOS gate for 2-input Nand & 2-input Nor gates ? 11) What are synthesizable and unsynthesizable constructs in Verilog? which one will be used when ? 12) Write verilog code for up-down counter? 14) Why Nand gate is preferable over Nor gate ? 15) Draw 3-bit Ring and Johnson Counter along with their States ?