Tessolve Semiconductors -Fresher (Validation Engineer)

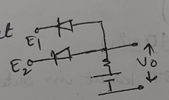

1. Round 1 1. Problems on Equivalent Resistance 2 Operation of CMOS Inverter 3. Problems on Transient, Steady state Analysis 4. Problems on calculating Equivalent Resistance in Op-Amp circuits 5. What is loading effect? 6. Operation of Inverter with R in place of pmos & NMOS , disadvantage in connecting in that way? 7. Latch and Flip-flop difference 8. What is test Engineer Job Role. 9. Problems on Expected Clock period to overcome Setup violation 10. Ideal characteristics of Op-Amp. ROUND 2(45min) 1. W hat it diode, operation of diode 2. what is transistor, what happens if voltage is increased ? 3. Avalanche Breakdown 4. Applications of diode 5. Identify Essential Prime Implicants (EPI), Prime Implicants in given problems 7. Can Flip flop be built with Latch ? 8. Can Latch be built with clock? 9. What is kelvin Connection ? 10. Uses of Buffer ? 11. Draw Inverting, non-Inverting Integrator, Different...