Tessolve Semiconductors -Fresher (Validation Engineer)

1. Round 1

1.Problems on Equivalent Resistance

2 Operation of CMOS Inverter

3. Problems on Transient, Steady state Analysis

4. Problems on calculating Equivalent Resistance in Op-Amp circuits

5. What is loading effect?

6. Operation of Inverter with R in place of pmos & NMOS , disadvantage in connecting in that way?

7. Latch and Flip-flop difference

8. What is test Engineer Job Role.

9. Problems on Expected Clock period to overcome Setup violation

10. Ideal characteristics of Op-Amp.

ROUND 2(45min)

1. What it diode, operation of diode

2. what is transistor, what happens if voltage is increased ?

3. Avalanche Breakdown

4. Applications of diode

5. Identify Essential Prime Implicants (EPI), Prime Implicants in given problems

7. Can Flip flop be built with Latch ?

8. Can Latch be built with clock?

9. What is kelvin Connection ?

10. Uses of Buffer ?

11. Draw Inverting, non-Inverting Integrator, Differentiator using op-amp & output Voltage formulas for the same

12. Ideal Characteristics of Op-Amp

13. Resolution of 8 bit input with 10V as input Voltage

14. Setup / hold timing definitions.

15. what happens when Depletion layer increases, comment on Barrier Potential

16. Expand MOSFET types

I7. Operation of Cmos inverter

18. what happens if NMOS, PMDS are interchanged in Inverter?

19. explain DẠC, ADC

2 Operation of CMOS Inverter

3. Problems on Transient, Steady state Analysis

4. Problems on calculating Equivalent Resistance in Op-Amp circuits

5. What is loading effect?

6. Operation of Inverter with R in place of pmos & NMOS , disadvantage in connecting in that way?

7. Latch and Flip-flop difference

8. What is test Engineer Job Role.

9. Problems on Expected Clock period to overcome Setup violation

10. Ideal characteristics of Op-Amp.

1. What it diode, operation of diode

4. Applications of diode

5. Identify Essential Prime Implicants (EPI), Prime Implicants in given problems

7. Can Flip flop be built with Latch ?

9. What is kelvin Connection ?

10. Uses of Buffer ?

11. Draw Inverting, non-Inverting Integrator, Differentiator using op-amp & output Voltage formulas for the same

12. Ideal Characteristics of Op-Amp

13. Resolution of 8 bit input with 10V as input Voltage

14. Setup / hold timing definitions.

15. what happens when Depletion layer increases, comment on Barrier Potential

16. Expand MOSFET types

I7. Operation of Cmos inverter

18. what happens if NMOS, PMDS are interchanged in Inverter?

19. explain DẠC, ADC

Round 3

3.Draw the current flow direction in cmos Inverter when ON, OFF

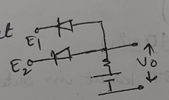

4. Output Range of Voltage across resistor of following circuit with 20V sine wave as input

5 what is Aliasing effect.

6. Transmitter, Receiver operation

7. Draw LPF, graph

8. what circuit must be used to get 10 outputs from 1 input

Comments

Post a Comment